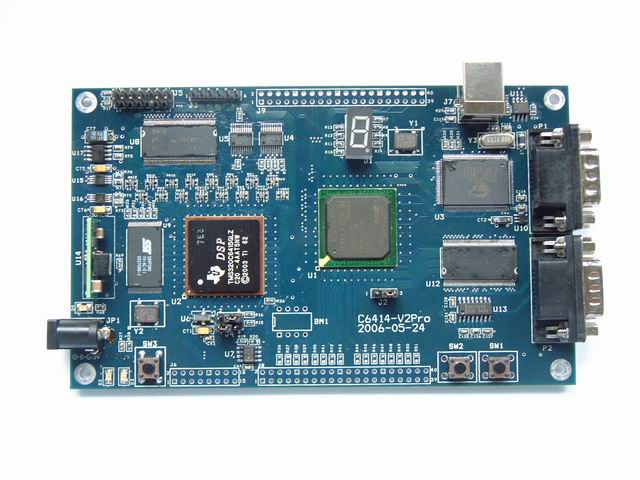

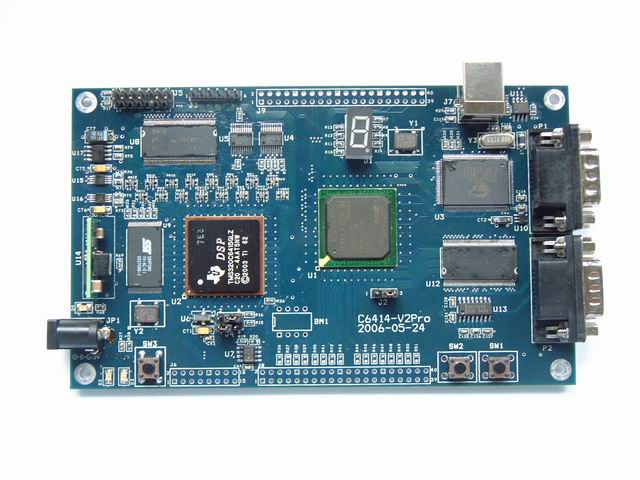

TMS320C6414 + XC2VP7

��ܰ�

��ʵ��ͼƬ��

����Ҫ��ɫ��

l ����TI��˾C6xϵ��DSP�е�TMS320C6414оƬ��ʱ��Ƶ��Ϊ600M Hz��������Ϊ1GHz��;

l C6414Ƭ���Դ��ṩ8M bit��������ݴ洢�����ֵ�Ӧ��ֻ��ʹ�ø��ٵ�Ƭ�ڴ洢���Ϳ����;

l C6414��EMIFA��ȫ�����ݡ�4����ַ�ߡ�3��Ƭѡ����д�ź�������FPGA

l C6414�ⲿ��չ128M bit

SDRAM;

l C6414�ⲿ��չ8M bit Flash Rom, �ܽ�����̻���Flash������Flash�ϵ�����;

l C6414�ṩ2·McBSP����;

l ����Xilinx��˾Virtex2 Proϵ��FPGA��100���ŵ�XC2VP7 �CFG456оƬ��Ƭ����Դ�dz��ḻ��Select Ram������576K bit�����ҿ����ó�˫��RAM��FIFO�������ⲿ����Ϳ���ʵ�ָ������ݲɼ�;

l FPGA�ڼ�����ǿ���PowerPC CPUӲ�ˣ�ʱ��Ƶ��300MHz;

l FPGA��Ƕ��Xilinx��˾MicroBlaze CPU���˼�UART��I2C��SDRAM�������ȶ���IP�ˣ�ʵ��ϵͳоƬ��SOC��;

l FPGA��չ128M bit

SDRAM;

l FPGA�ṩ64��ͨ��IO������32��IO�����ó�16·LVDS���;

l LVDS��ִ����ٶȿɴ�800M bit/s�����ô���LVDS��ִ���ɴ����ٲ��д��������������Ŀ��������������������;

l FPGA��չ��һ��RS232���ڣ�һ��4λ�IJ��뿪�أ�������ť��һ��7�������;

l ������CYPRESS��˾��128�ŵ�CY7C68013 -128 USB2.0оƬ;

l 68013оƬ�����ݡ���ַ��ȫ������FPGA�����Խ�FPGAƬ�ڵĴ洢��ӳ��Ϊ68013�洢����Ϊ�̼��ṩ����ij������ݿռ�;

l 68013оƬ��Slave FIFO(GPIF)�ӿ�������FPGA;

l 68013оƬ��չ��һ��RS232���ڣ��ɶ�68013�̼����е������ϵ����

l DSP��PC����ͨ��USB�ӿڸ���ͨ�ţ������ʿɴ�32M �ֽ�/��;

����ʾ���ӡ�

1. DSP��PC�������ͨ��

USBͨ��Slave

FIFO�ӿ���DSP����һ����������������д��FPGA�ڵ����FIFO��ͬʱ68013����һ��DSP�жϣ�DSP��Ӧ�жϣ���DMA��ʽ��FIFO��ȡ�������ִ����Ӧ�������DMA��ʽ������д��FPGA�ڵ�����FIFO��FPGA�ڵĿ����������ݴ�����FIFO������д��68013оƬ���ڲ�FIFO��

2. FPGA��PowerPCӲ�˹�����ʾ

����XILINX��˾��Ƕ��ʽϵͳ��������EDK7.1����FPGA�ڼ�����CPUӲ��PowerPC��SDRAM��������UART���ڡ���ʱ��������ܿ��Ƶ�IP�ˣ�����ͨ�����ں�PC��ͨ�ţ���дFPGA��չ��SDRAM�������������ʾ�ȡ�

3. LVDS���д�����ʾ

LVDS���д���ͨ������ת�����������ݴ��л���ͨ��LVDS��ַ�ʽ���ٴ��䣬�����������˴�������Ŀ��������˿ɿ��ԡ�����˵��������Ҫ��������ݿ�����16λ��ʱ��Ƶ��Ϊ10MHz����ͳ�IJ��д��䷽ʽ��Ҫ 16λ������ + 1λʱ�� + 1λͬ������18���ߣ������д��䷽ʽͨ����ߴ���Ƶ�ʺ�ʱ��������ͬʱ����ķ�ʽ��ֻ��1λ�����ߺ�1λʱ���ߣ���2���ߣ�ʱ��Ƶ��Ϊ80MHz��

����ʾ��Ҫ��̨PC�������鿪���塣PC��1ͨ��USB�ӿڽ�ͼ�����ݷ��͵�������1��������1��ɲ���ת����������LVDS���в�ַ�ʽ���͵�������2��������2���д���ת��ͨ��USB�ӿڰ����ݷ��͵�PC��2��PC��2��ʾ���յ���ͼ�����ݡ�

4. 68013����ͨ�źͶϵ㡢��������

ͨ��68013�Ĵ��ں�PC��ͨ�ţ����ؼ�س���ʵ�ֶ�68013����Ķϵ㡢�������ԡ�

5. DSP����̻�

��DSP����̻���Flash

Rom�У�ʵ���ϵ������������̻����̼���ݣ�����Ҫ��Դ��������κ��ġ�

���ṩ���ϡ�

1. ��ʾ����Դ����

2. ��·��ԭ��ͼ��pdf��ʽ��

3. Xilinx

FPGA��������ISE7.1

4. Xilinx Ƕ��ʽϵͳ�������� EDK7.1

5. TI

DSP��������CCS3.1

6. ��Ƭ����������Keil

7.02 |